【摘要】 陶瓷/导电填料虽然可以大幅提高复合材料的介电常数,但这些填料可能形成载流子的导电通路,使低频下高电导率和介电损耗成为严重的问题。

本期我们重点介绍多层结构对材料介电性能的影响。

陶瓷/导电填料虽然可以大幅提高复合材料的介电常数,但这些填料可能形成载流子的导电通路,使低频下高电导率和介电损耗成为严重的问题。制备多层结构的薄膜是解决这一问题的有效方法。多层结构可以有效地防止整个薄膜形成导电网络,从而抑制介电损耗。在多层结构中,每一层都起到各自的作用,包括实现有效绝缘、增加界面极化、优异热导性等,以及界面势垒效应带来的高击穿强度。

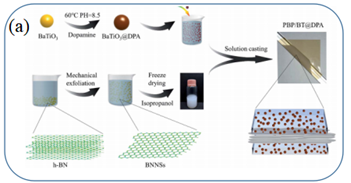

图1(a)制备PBP/BT@DPA三明治结构薄膜.

磺化聚芳醚腈(SPEN)、氮化硼纳米片(BNNS)等,这些物质都具有绝缘性,可用作绝缘层使用以发挥对介电损耗的高效抑制作用。Chen等以掺杂10wt%多巴胺包覆钛酸钡的聚(偏氟乙烯-六氟丙烯)(HFP/BT@DPA)材料作外层,0.75wt%氮化硼纳米片(BNNs)作中间层(图1a)制备具有三明治结构的薄膜,外层混合物在提高介电常数(100 Hz,k = 11)的同时,也因为陶瓷颗粒的聚集产生孔隙和MWS界面极化,造成介电损耗增加,通过引入绝缘的中夹层阻碍了电分支的生长,抑制泄露电流密度,从而抑制了介电损耗的增长,但这种抑制作用在高频下不明显(100 Hz, tanδ < 0.1; 106 Hz, tanδ=0.3)。此外,绝缘层的固有低介电常数可以限制复合材料的电能密度(8.37 J·cm-3)。

本期由于版面原因,更多关于高介电材料的知识我们下一期再介绍。

参考文献

[1] Chen F J,Zhou Y J,Guo J M,Sun S,Zhao Y T,Yang Y J,Xu J H. RSC Advances,2020,10,(4):2295.

[2] Feng Y,Li M-L,Li W-L,Zhang T-D,Zhao Y,Fei W-D. Applied Physics Letters,2018,112,(2):022901.

科学指南针提供各类科研测试服务,愿您总能获得想要的结果。我们收到的测试样品来自各地,种类繁多,如果我们回复不及时,还请再次联系,或直接语音电话联络,若您对我们的服务不满意,或对测试结果有疑问,请果断联系我们或直接拨打400-831-0631,我们对每个数据及结果,会负责到底!科研可能很苦,但坚持一定很苦,愿您顺利!

免责声明:部分文章整合自网络,因内容庞杂无法联系到全部作者,如有侵权,请联系删除,我们会在第一时间予以答复,万分感谢。

您已经拒绝加入团体

您已经拒绝加入团体

2022-04-28

2022-04-28

4341

4341

0

0